در حالی که عمده توجه TSMC معطوف به گره های پیشرفته آن مانند N3E و N2 است، تعداد زیادی از تراشه ها با استفاده از فناوری های فرآیندی بالغ تر و اثبات شده تر برای سال های آینده ساخته خواهند شد. به همین دلیل است که TSMC به اصلاح گرههای موجود خود از جمله ارائههای نسل فعلی کلاس 5 نانومتری خود ادامه داده است. به همین منظور، در سمپوزیوم فناوری آمریکای شمالی 2024، این شرکت یک گره جدید و بهینه کلاس 5 نانومتری را معرفی کرد: N4C.

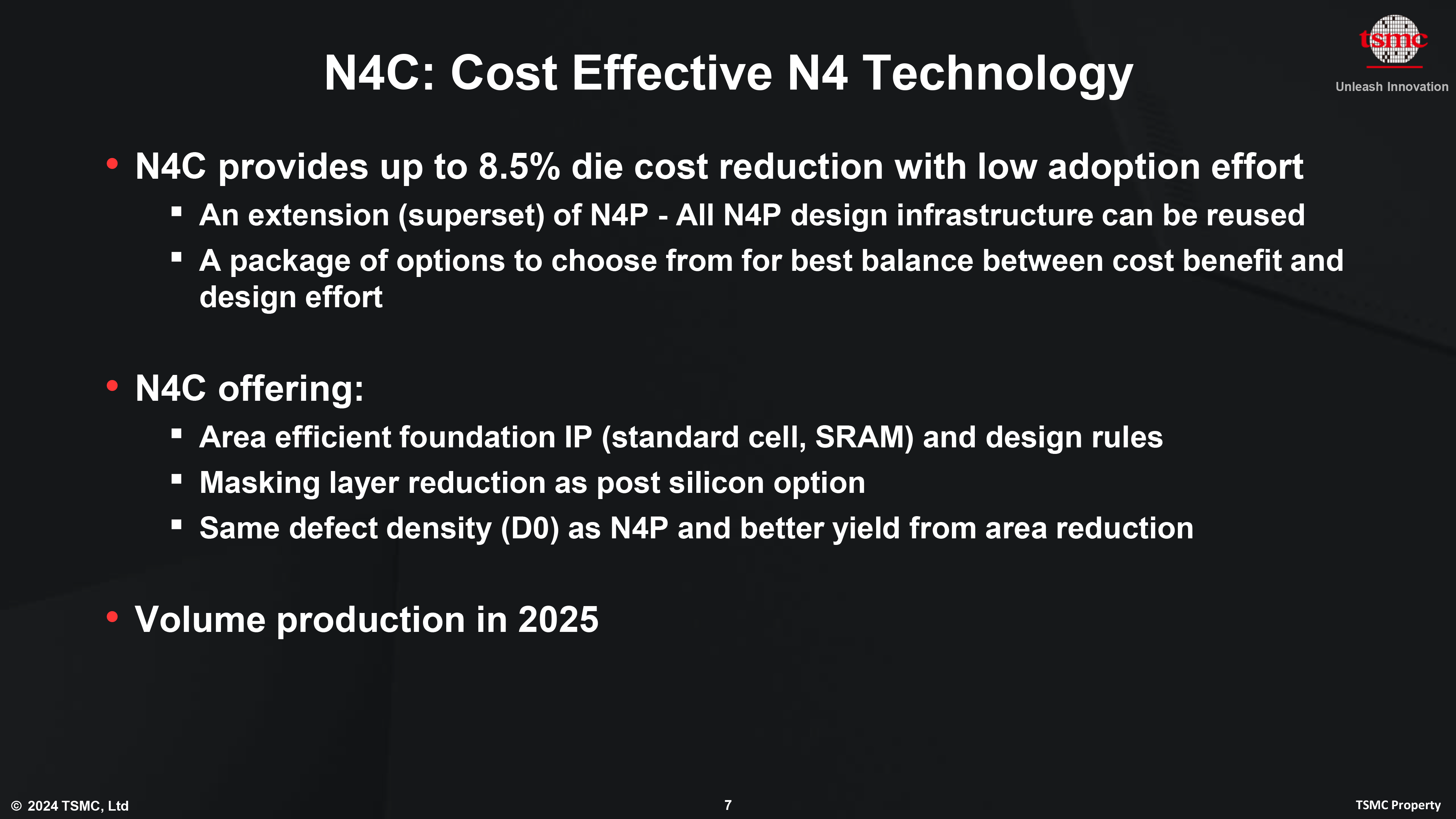

فرآیند N4C TSMC متعلق به خانواده گرههای fab کلاس 5 نانومتری این شرکت است و سوپرمجموعهای از N4P، پیشرفتهترین فناوری در آن خانواده است. در تلاش برای کاهش بیشتر هزینههای تولید 5 نانومتری، برای TSMC چندین تغییر را برای N4C اعمال میکند، از جمله معماری مجدد سلول استاندارد و سلول SRAM، تغییر برخی قوانین طراحی و کاهش تعداد لایههای پوشش. در نتیجه این پیشرفتها، شرکت انتظار دارد N4C به اندازههای قالب کوچکتر و همچنین کاهش پیچیدگی تولید دست یابد که به نوبه خود هزینههای قالب را تا 8.5 درصد کاهش میدهد. علاوه بر این، با همان نرخ تراکم نقص در سطح ویفر مانند N4P، N4C به لطف کاهش سطح قالب، عملکرد عملکردی بالاتری را ارائه می دهد.

کوین ژانگ، معاون توسعه کسب و کار در TSMC می گوید: «بنابراین، ما با فناوری های 5 نانومتری و 4 نانومتری خود تمام نشده ایم. “از N5 تا N4، ما به 4% کاهش تراکم اپتیکال دست یافته ایم و به بهبود عملکرد ترانزیستور ادامه می دهیم. اکنون N4C را به مجموعه فناوری 4 نانومتری خود وارد می کنیم. N4C به مشتریان ما این امکان را می دهد که هزینه های خود را با حذف برخی از موارد کاهش دهند. ماسکها و همچنین بهبود طراحی IP اصلی مانند سلول استاندارد و SRAM برای کاهش بیشتر هزینه مالکیت در سطح کلی محصول.”

TSMC میگوید که N4C میتواند از زیرساخت طراحی مشابه N4P استفاده کند، اگرچه مشخص نیست که آیا IP N5 و N4P میتوانند دوباره برای تراشههای مبتنی بر N4C استفاده شوند یا خیر. در همین حال، TSMC نشان میدهد که گزینههای مختلفی را برای سازندگان تراشه ارائه میکند تا تعادل مناسب بین مزایای هزینه و تلاش طراحی را پیدا کنند، بنابراین شرکتهایی که علاقهمند به استفاده از فناوریهای فرآیند کلاس 4 نانومتری هستند، میتوانند N4C را به کار گیرند.

توسعه N4C در حالی صورت میگیرد که بسیاری از مشتریان طراحی تراشه TSMC در حال آمادهسازی برای عرضه تراشههای مبتنی بر نسل نهایی فناوری فرآیند FinFET این شرکت، سری 3 نانومتری N3 هستند. در حالی که انتظار می رود N3 خانواده موفقی باشد، هزینه های بالای N3B یک مسئله بوده است و تولید با کاهش عملکرد و به طور کلی بازده ترانزیستور مشخص می شود. در نتیجه، N4C میتواند به یک گره اصلی و با عمر طولانی در TSMC تبدیل شود و به عنوان یک مناسب برای مشتریانی که میخواهند به یک گره FinFET مقرونبهصرفهتر پایبند باشند، عمل میکند.

ژانگ گفت: “این یک پیشرفت بسیار مهم است، ما با مشتری خود کار می کنیم، اساساً برای استخراج ارزش بیشتر از سرمایه گذاری 4 نانومتری آنها.”

TSMC انتظار دارد تولید حجمی تراشه های N4C را در سال آینده آغاز کند. و با توجه به اینکه TSMC برای نزدیک به نیم دهه در آن نقطه کلاس 5 نانومتری تولید کرده است، N4C باید بتواند از نظر حجم و بازده به زمین برسد.

خواندن مرتبط

مرجع اخبار سخت افزار کامپیوترایران

تحریریه Techpowerup