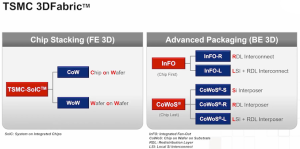

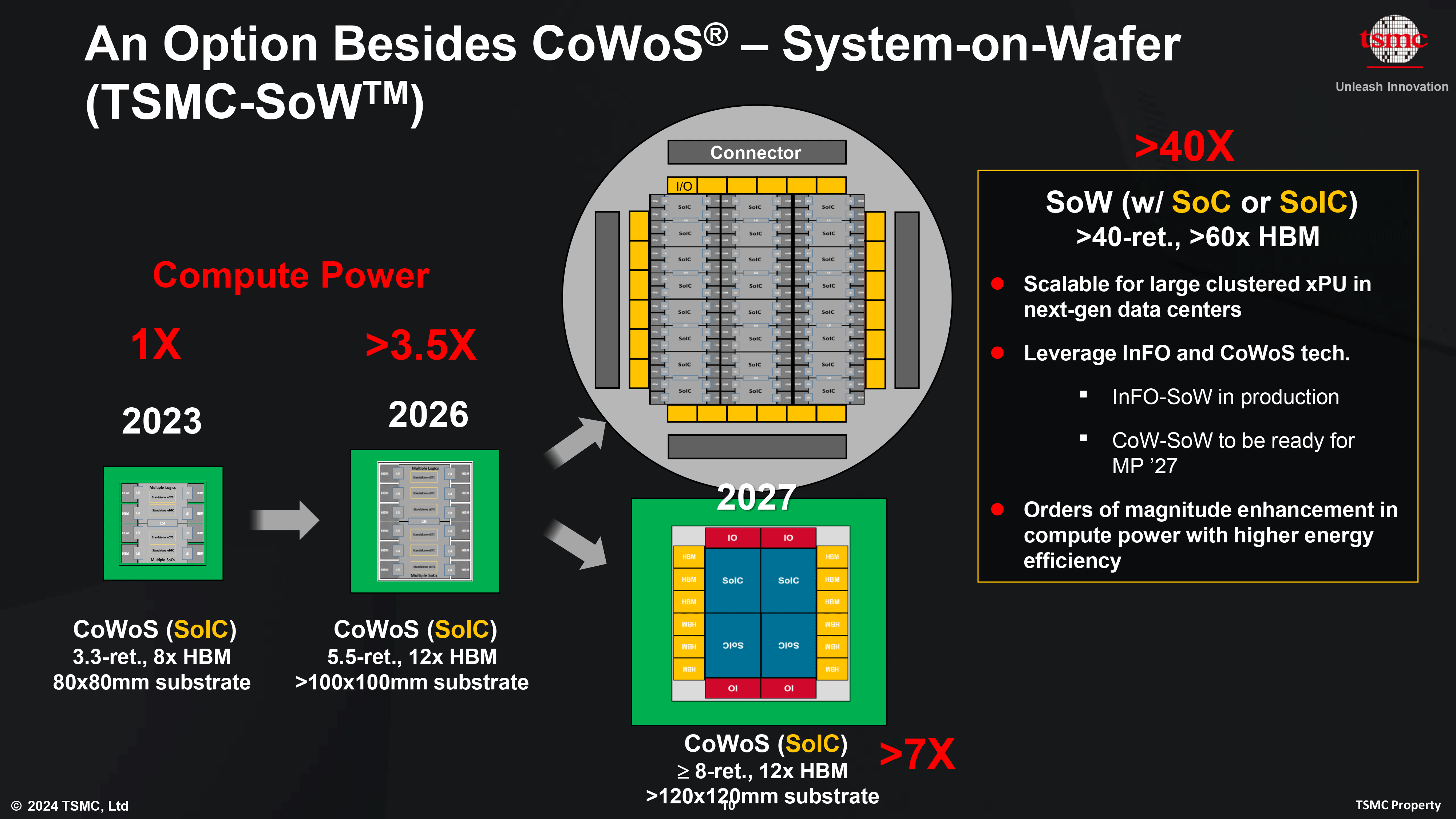

TSMC با ساخت تراشه های بزرگ غریبه نیست. علاوه بر محدودیت حدود 800 میلیمتر مربع در فرآیندهای منطقی عادی خود، این شرکت در حال حاضر تراشههای حتی بزرگتری را با نصب چندین قالب بر روی یک اینترپوزر سیلیکونی، با استفاده از فناوری تراشه روی ویفر روی بستر (CoWoS) تولید میکند. اما حتی با وجود CoWoS نسل کنونی که اجازه میدهد تا 3.3 برابر محدودیت شبکه TSMC به اینترپوزرها وارد شود، TSMC قصد دارد در پاسخ به تقاضای پیشبینیشده از سوی صنایع HPC و AI، بزرگتر بسازد. به همین منظور، هفته گذشته، به عنوان بخشی از سمپوزیوم فناوری آمریکای شمالی این شرکت، TSMC اعلام کرد که در حال توسعه ابزاری برای ساخت اینترپوزرهایی با اندازه فوق العاده است که می تواند به بیش از 8 برابر حد مجاز شبکه برسد.

فناوری CoWoS نسل فعلی TSMC امکان ساخت interposer تا 2831 میلی متر را فراهم می کند.2 و این شرکت در حال حاضر می بیند که مشتریانی با طرح هایی با این محدودیت ها وارد می شوند. هر دو شتابدهنده MI300X Instinct AMD و شتابدهنده B200 آینده NVIDIA نمونههای بارز این موضوع هستند، زیرا چیپلتهای منطقی عظیمی را در خود جای دادهاند (در صورت وجود محصول AMD روی هم چیده شدهاند) و در مجموع هشت پشته حافظه HBM3/HBM3E دارند. فضای کلی ارائه شده توسط interposer به این پردازنده ها عملکرد فوق العاده ای می دهد، اما توسعه دهندگان تراشه می خواهند همچنان قدرتمندتر باشند. و برای اینکه هر چه سریعتر به آنجا برسند، باید بزرگتر شوند تا چیپلت های منطقی بیشتر و پشته های حافظه بیشتری را ترکیب کنند.

برای نسل بعدی محصول CoWoS خود که قرار است در سال 2026 عرضه شود، TSMC قصد دارد CoWoS_L را منتشر کند که حداکثر اندازه اینترپوزر تقریباً 5.5 برابر یک ماسک نوری و در مجموع 4719 میلی متر مربع را ارائه می دهد. این بسته نسل بعدی تا 12 پشته حافظه HBM را پشتیبانی می کند و نیاز به بستر بزرگتر با ابعاد 100×100 میلی متر دارد. همراه با بهبود گره های فرآیندی طی چند سال آینده، و TSMC انتظار دارد تراشه های مبتنی بر این نسل از CoWoS عملکردی بهتر از 3.5 برابر تراشه های CoWoS نسل فعلی ارائه دهند.

دورتر از این خط، در سال 2027 TSMC قصد دارد نسخهای از CoWoS را معرفی کند که اجازه میدهد تا 8 برابر بزرگتر از حد مجاز شبکههای داخلی وارد شوند. این فضای کافی 6864 میلیمتر مربع را برای چیپلتها روی بستری با ابعاد 120×120 میلیمتر ارائه میکند. TSMC در نظر دارد از این فناوری برای طرحهایی استفاده کند که چهار تراشه سیستمهای روی هم یکپارچه (SoIC) را با 12 پشته حافظه HBM4 و قالبهای ورودی/خروجی اضافی ادغام میکنند. TSMC تقریباً پیشبینی میکند که این امر به طراحان تراشه امکان میدهد یک بار دیگر عملکرد را دو برابر کنند و تراشههایی تولید کنند که عملکردی ۷ برابری از تراشههای نسل فعلی داشته باشند.

البته، ساخت چنین تراشه های بزرگ مجموعه ای از پیامدهای خود را به همراه خواهد داشت، فراتر از آنچه TSMC باید با آن مقابله کند. توانمندسازی طراحان تراشه برای ساخت چنین پردازندههای بزرگی بر طراحی سیستم و همچنین نحوه تطبیق مراکز داده با این سیستمها تأثیر میگذارد. زیرلایه 100×100 میلیمتری TSMC تا سقف ضریب فرم OAM 2.0 که اندازه ماژولهای آن برای شروع 102×165 میلیمتر است، حرکت میکند. و اگر آن نسل از CoWoS ضریب فرم OAM فعلی را شکست ندهد، تراشههای ۱۲۰×۱۲۰ میلیمتری قطعاً این کار را خواهند کرد. و البته، تمام این سیلیکون اضافی به قدرت و خنککننده اضافی نیاز دارد، به همین دلیل است که ما شاهد آمادهسازی فروشندگان سختافزار برای نحوه خنک کردن تراشههای چند کیلوواتی با بررسی خنکسازی مایع و غوطهوری هستیم.

در نهایت، حتی اگر قانون مور از نظر ارائه بهبود تراکم ترانزیستور تا حد خزیدن کاهش یافته باشد، CoWoS برای تولید تراشههایی با تعداد ترانزیستورهای بیشتری ارائه میکند. بنابراین با توجه به اینکه TSMC برای ارائه اینترپوزرها و زیرلایه هایی با بیش از دو برابر مساحت راه حل های امروزی تنظیم شده است، تراشه های بزرگی که برای سیستم های HPC در نظر گرفته شده اند فقط از نظر عملکرد و اندازه به رشد خود ادامه می دهند.

خواندن مرتبط

مرجع اخبار سخت افزار کامپیوترایران

تحریریه Techpowerup