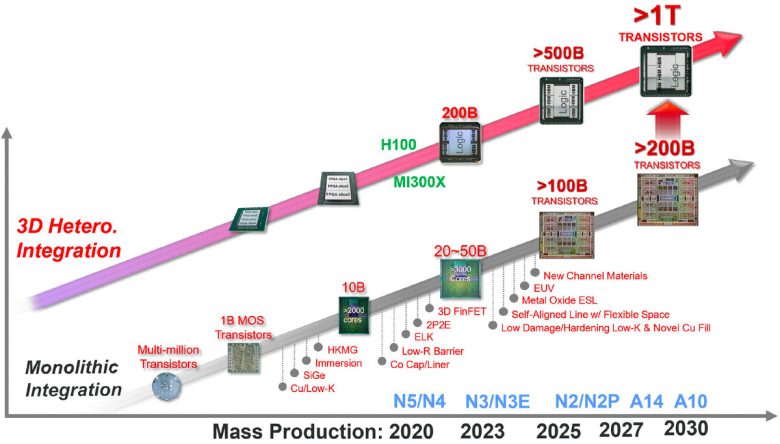

با این حال، نقشه راه TSMC بیش از دو برابر کردن این رقم را می طلبد، ابتدا با بیش از 100 میلیارد طرح ترانزیستور یکپارچه، سپس در نهایت 200 میلیارد. البته، با افزایش اندازه قالب، بازدهی سختتر میشود و اینجاست که بستهبندی پیشرفته چیپستهای کوچکتر بسیار مهم میشود. ماژول های چند تراشه ای مانند MI300X AMD و Ponte Vecchio اینتل در حال حاضر شامل ده ها کاشی هستند که PVC دارای 47 کاشی است. TSMC در حال بررسی این توسعه در بستههای تراشههایی است که بیش از یک تریلیون ترانزیستور را از طریق CoWoS، InFO، انباشته سه بعدی و بسیاری از فناوریهای دیگر در خود جای میدهند. اگرچه سرعت مقیاسبندی اخیراً کاهش یافته است، TSMC به توانایی خود برای دستیابی به پیشرفتهای بستهبندی و فرآیند برای برآورده کردن نیازهای تراکم آتی اطمینان دارد. سرمایه گذاری مستمر کارخانه ریخته گری پیشرفت را در استفاده از قابلیت های نیمه هادی های نسل بعدی تضمین می کند. اما فیزیک در نهایت ضرب الاجل ها را تعیین می کند، مهم نیست که چقدر تهاجمی باشند.

مرجع اخبار سخت افزار کامپیوترایران

تحریریه Techpowerup